基于单片机的数字移相器的设计(锁相环)

来源:56doc.com 资料编号:5D1666 资料等级:★★★★★ %E8%B5%84%E6%96%99%E7%BC%96%E5%8F%B7%EF%BC%9A5D1666

资料以网页介绍的为准,下载后不会有水印.资料仅供学习参考之用. 密 保 惠 帮助

资料介绍

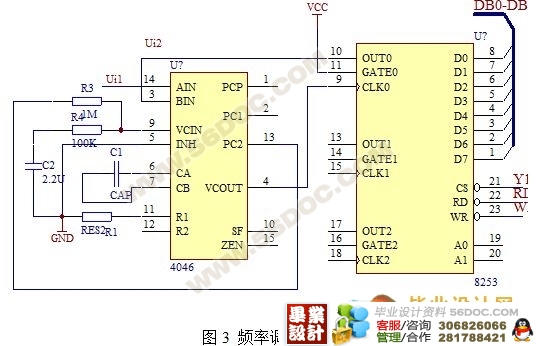

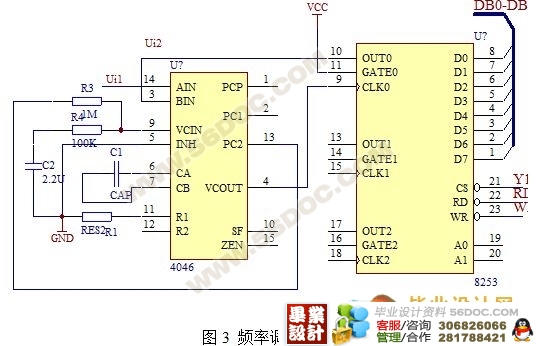

摘 要: 介绍基于单片机实现两路频信号间数字移相,并利用锁相环和定时/计数器8253改变两路信号频率的方法。(毕业设计网 )

关键词:移相;单片机;锁相环;地址计数器

题需要完成的任务:

采用DDS技术生成两路正弦波信号,并通过改变存储器中数据读取的起始地址来实现数字移相的功能。

原理:数字移相方法――先将正弦波信号数字化,并形成一张数据表存入ROM芯片中,此后可通过两片D/A转换芯片,在单片机控制下连续地循环输出该数据表,就可以获得两路正弦波信号。当两片D/A所获得序列不同时,两路信号便产生相位差。

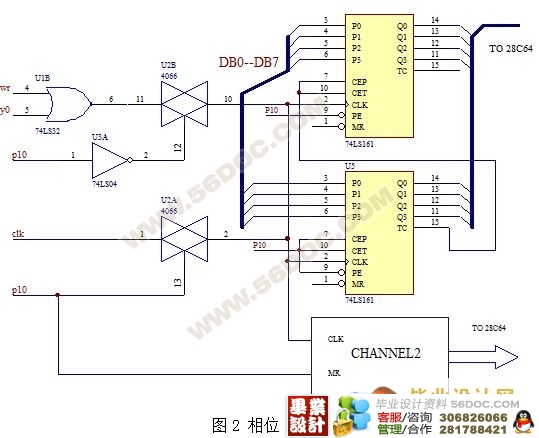

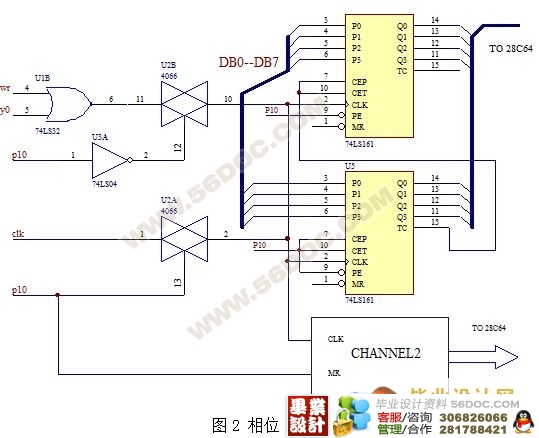

相位差产生电路

选用8K的EEPROM存储器28C64对正弦波信号的量化数据表进行存储,数据表中数据共有256个,每两个相邻数据之间的相位差为3600÷256=1.40度,只需要改变程序中寄存器R5中的值就可改变两路正弦波的相位差。正弦波信号的量化数据表如下:

TAB: DB 80H,83H,86H,89H,90H,93H,96H

DB 99H,9CH,9FH,A2H,A5H,A8H,ABH,AEH

DB B1H,B4H,B7H,BAH,BCH,BFH,C2H,C5H

DB C7H,CAH,CCH,CPH,D1H,D4H,D6H,D8H

DB DAH,DDH,DFH,E1H,E3H,E5H,E7H,E9H

DB EAH,ECH,EEH,EFH,F1H,F2H,F4H,F5H

DB F6H,F7H,F8H,F9H,FAH,FBH,FCH,FDH

DB FDH,FEH,FFH,FFH,FFH,FFH,FFH,FFH

DB FFH,FFH,FFH,FFH,FFH,FFH,FEH,FDH

DB FDH,FCH,FBH,FAH,F9H,F8H,F7H,F6H

DB F5H,F4H,F2H,F1H,EFH,EEH,ECH,EAH

DB E9H,E7H,E5H,E3H,E1H,DFH,DDH,DAH

DB D8H,D6H, D4H,D1H,CFH,CCH,CAH,C7H

DB C5H,C2H,BFH,BCH,BAH,B7H,B4H,B1H

DB AEH,ABH,A8H,A5H,A2H,9FH,9CH,99H

DB 96H,93H,90H,8DH,89H,86H,83H,8OH

DB 80H,7CH,79H,76H,72H,6FH,6CH,69H

DB 66H,63H,60H,5DH,5AH,57H,55H,51H

DB 4EH,4CH,48H,45H,43H,40H,3DH,3AH

DB 38H,35H,33H,30H,2EH,2BH,29H,27H

DB 25H,22H,20H,1EH,1CH,1AH,18H,16H

DB 15H,13H,11H,10H,0EH,0DH,0BH,0AH

DB 09H,08H,07H,06H,05H,04H,03H,02H

DB 02H,01H,00H,00H,00H,00H,00H,00H

DB 00H,00H,00H,00H,00H,00H,01H,02H

DB 02H,03H,04H,05H,06H,07H,08H,09H

DB 0AH,0BH,0DH,0EH,10H,11H,13H,15H

DB 16H,18H,1AH,1CH,1EH,20H,22H,25H

DB 27H,29H,2BH,2EH,30H,33H,35H,38H

DB 3AH,3DH,40H,43H,45H,48H,4CH,4EH

DB 51H,55H,57H,5AH,5DH,60H,63H,66H

DB 69H,6CH,6FH,72H,76H,79H,7CH,80H

74LS161功能表

清除 PT PE CP DCBA QDQCQBQA

0 X x x xxxx 0000

1 0 1 x xxxx 保持原状态

1 0 0 ↑ dcba dcba(预置)

1 1 1 ↑ xxxx 计数

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出QDQCQBQA立即为全“0”,这个时候为异步复位功能。当CR=“1”且PE=PT=“0”时,在CP信号上升沿作用后,74LS161输出端QDQCQBQA的状态分别与并行数据输入端QDQCQBQA的状态一样,为同步置数功能。而只有当CR=PE=PT=“1”、CP脉冲上升沿作用后,计数器加1。

相位差预置电路如图2所示:当P1.0=0时,通道2的两个计数器清零,使该路的初始相位为零。此时模拟开关CD4066的U2A关闭,地址计数脉冲不能进入两路地址计数器,同时模拟开关CD4066的U2B打开。此时通道1的两片74LS161的CET=CEP=0,PE=0,处于预置状态(可参见74LS161功能表),由WR与选通信号Y.0经过或门U1B产生一个上升沿脉冲,送入通道1的两个74LS161的时钟端CP时,单片机则通过数据线DB0~DB7将初始相位差预置到两个地址计数器的输出端。然后P1.0=1,打开模拟开关U2A使时钟脉冲同时送入两路地址计数器,从而产生某一相位差的两路正弦信号。

毕业设计说明书目录

1 引言………………………………………………………………………………

2 方案设计及论证…………………………………………………………………

2.1 数字移相形式方案的选择…………………………………………………..

2.2 键盘方案的选择……………………………………………………………..

3 系统框图及工作原理……………………………………………………………

4 系统分立模块设计及工作原理…………………………………………………

4.1 相位差产生电路……………………………………………………………..

4.2 频率调整电路………………………………………………………………..

4.3 存储器与模数转换电路……………………………………………………..

4.4 键盘与显示电路……………………………………………………………..

5 芯片介绍…………………………………………………………………………

5.1 介绍AT89C52单片机……………………………………………………….

5.2 8253可编程定时/计数器…………………………………………………...

5.3 CD4046锁相环……………………………………………………………...

5.4 四位可预置计数器74LS161………………………………………………..

5.5 28C64存储器………………………………………………………………..

5.6 D/A0832模数转换…………………………………………………………..

(毕业设计网 )

5.7 555定时器…………………………………………………………………...

6 软件设计…………………………………………………………………………..

7参考文献…………………………………………………………………………...

8附录………………………………………………………………………………..

9毕业设计总结…………………………………………………………………...... |