基于EDA和单片机技术的逻辑分析仪设计课件

来源:56doc.com 资料编号:5D1687 资料等级:★★★★★ %E8%B5%84%E6%96%99%E7%BC%96%E5%8F%B7%EF%BC%9A5D1687

资料介绍

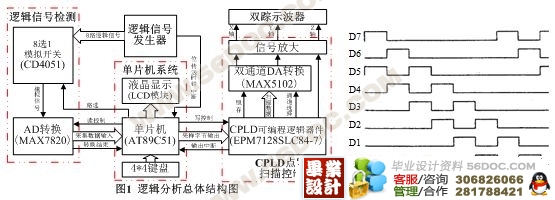

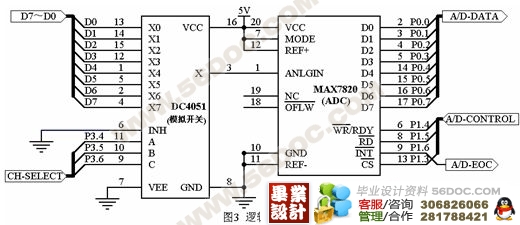

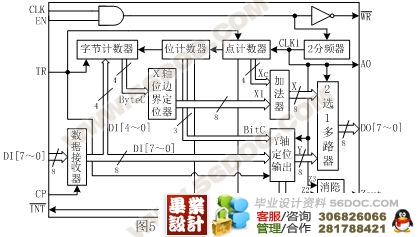

摘要:本设计采用单片机控制8路逻辑信号电平采集;采用EDA技术设计的CPLD芯片处理逻辑信号,控制点阵扫描和分析结果在示波器上显示;单片机和CPLD间采用中断方式交换数据。该设计具有1、3级触发方式,触发字位置和浮动时标线显示等功能,以及友好操作界面和波形稳定显示等特点,并拓宽示波器使用功能。 关键字:点阵扫描控制;逻辑分析;CPLD;VHDL编程 【Abstract】This design uses the one-chip microcomputer to be controlled gathering of logical signal levels of 8 tunnels, Use CPLD's chip of EDA's technical design to the logic signal processing and Control scanning to the lattice signal and The result of display analysis on the oscillograph , Use the interrupt mode exchange data between one-chip microcomputer and CPLD. this design has 1 and 3 grade of method of activation , trigger word seat display and time to be marked thread display etc. merit ability,As well as friendly operation interface and waveform stabilization what shows etc. characteristic , And widen the oscillograph use merit ability . 【Key words】The lattice scanning control; The logical analysis; CPLD; VHDL's programming 软件设计 软件设计部分有逻辑信号检测及数据采集处理、键盘显示扫描处理、采样字节输出处理和CPLD内部结构设计VHDL(硬件描述语言)编程四部分。本文主要介绍逻辑信号检测及数据采集处理和CPLD结构设计VHDL编程部分。 逻辑信号检测及数据采集处理 逻辑信号检测及数据采集处理是通过单片机的INT1中断服务程序来完成。其中1级触发字逻辑信号检测中断服务程序和数据采集处理子程序流程如图6、图7所示。 当各项参数设定后,按“确认键”保存参数,并打开逻辑信号检测中断(INT1),关闭采样字节输出中断(INT0)。每次逻辑信号发生器的位传送时钟(B-CLK)触发一次逻辑信号检测中断服务程序的执行,每次服务程序执行要进行8次路选和8次AD转换启动,并分别检测转换结束状态和读取转换结果。每次逻辑信号检测中断服务,要调用8路逻辑信号数据采集处理子程序,将8路信号状态转换成1个采样字节,并存入采样数据区。当数据区存满后,关闭逻辑信号检测中断,打开采样字节输出中断,等待CPLD输出中断请求(CLPD-INT)。 本设计将单片机和EDA技术结合起来,简化了硬件结构,工作性能稳定,经过应用测试,达到了逻辑分析仪应有的功能要求。 通过本设计,笔者认为,运用EDA技术设计电路,设计者可专注于电路的行为和功能,而不必考虑电路如何实现及电路布线,并且可通过计算机进行设计效果的模拟和修改,为设计者提供了更广阔的设计空间。用单片机和EDA技术开发的电子产品,在功能、性能指标和开发效率等方面比传统的方法有明显的提高,而且成本降低。 参考文献:[1]顾乃级,孙续. 逻辑分析仪原理与应用[M]. 北京:人民邮电出版社,1973. [2]李华,MCS-51系列单片机实用接口技术[M]. 北京:北京航空航天大学出版社,1993. [3]潘松,黄继业. EDA技术实用教程[M]. 北京:科学出版社,2002.    |