摘 要

本论文的研究任务是用FPGA实现一个单片机内核。即使用硬件描述语言VHDL来实现整个系统的逻辑描述,所实现的指令系统与8051单片机的指令系统完全兼容。再以QuartusⅡ软件为工具,完成所有模块的软件仿真测试。

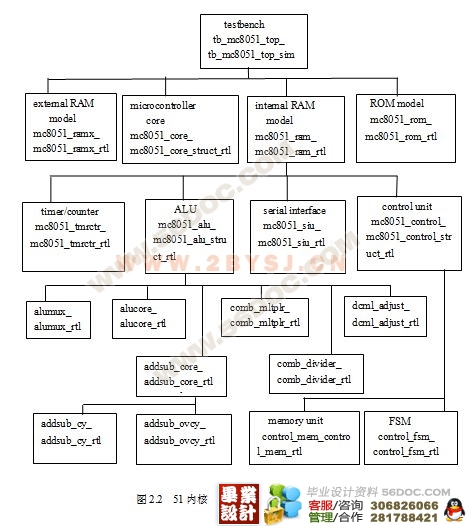

本文对8051单片机进行原理分析和特征提取,介绍了EDA开发工具以及本IP核的设计方案。利用自顶向下的设计方法把8051IP核划分成多个子模块,并在QuartusⅡ软件中分别用VHDL语言来完成各个子模块实现程序的编写。最后,采用原理图连接的方法把各个模块连接起来组成了完整的8051IP核。

设计完成后,在QuartusⅡ软件中对所设计的8051IP核进行验证,本文通过具体的实验来对8051IP核进行验证。

关键词:VHDL;8051单片机;FPGA

With a typical FPGA Implementation of the 51 core and test

Abstract

In this paper, the research is the realization of a microcontroller core FPGA. That is, the use of hardware description language VHDL to realize the logic described the system as a whole, achieved by the command system and the 8051 SCM system is fully compatible with the directive. Then Quartus Ⅱ software tools, complete all the modules of the software simulation tests.

In this paper, for 8051 SCM principles of analysis and feature extraction, introduced the EDA development tools and the IP core design. Use of top-down approach to the design of the 8051 IP divided into multiple sub-module, and Quartus Ⅱ software were used to complete all of VHDL module to achieve the preparation process. Finally, the principle of using the method to connect the various modules to form a complete 8051 IP nuclear.

Upon completion of the design, in the Quartus Ⅱ software designed by the 8051 IP nuclear verification, the paper through specific experiments to the 8051 IP nuclear verification.

Key Words: VHDL;8051IPCORE;FPGA

本论文的研究任务是用FPGA实现一个单片机内核,即使用硬件描述语言VHDL来实现整个系统的逻辑描述,开发出能够应用于FPGA的8051IP核,所实现的指令系统与8051单片机的指令系统完全兼容。再以QuartusⅡ软件和 NIOS II处理器为工具, 设计led流水灯控制来验证8051 IP核。

论文主要工作

(1) 本文详细介绍了使用VHDL语言来设计和实现与标准8051单片机的功能和指令相兼容的8051IP核的设计方法、设计思路和实现过程。

(2) 用TOP-DOWN方法自顶向下将整个8051IP核设计细化为多个子模块并用VHDL语言实现了各个模块的代码设计和8051IP核的整体设计。

(3) 在EDA工具QuartusII 5.0平台上以及NiosII处理器 对所设计的8051IP核进行了整体实际验证。

目 录 15000字

摘 要 I

Abstract II

引 言 1

1 绪论 2

1.1 课题研究的背景 2

1.2 选题的依据和意义 3

1.3 本论文的主要工作 4

2 8051结构分析及8051IP核的总体规划 5

2.1 8051单片机内部结构原理 5

2.1.1 CPU结构 5

2.1.2 存储器结构 6

2.1.3 定时器/计数器 6

2.1.4 中断系统 7

2.1.5 I/O端口 7

2.2 8051IP核的顶层设计和系统模块的划分 7

2.2.1 自顶向下的设计方法 8

2.2.2 8051IP核的具体分割 8

2.3 8051IP核的设计工具介绍 10

2.3.1 VHDL语言介绍 10

2.3.2 QuartusII软件及各模块在其中的开发流程介绍 10

3 8051IP核部分模块的具体设计 12

3.1 alu模块的实现 12

3.1.1 alucore逻辑运算块 13

3.1.2 addsub加减法模块 16

3.2 存储器模块的实现 23

3.3 8051IP模块的总体实现 26

4 检验8051IP核 28

(毕业设计)

4.1 流水灯控制原理 28

4.2 流水灯控制框图 28

4.3 流水灯控制硬件设计部分 29

4.4 流水灯控制软件设计部分 30

4.5 结果显示 32

5 结论 33

5.1 论文主要工作 33

5.2 论文的后续研究和展望 33

参 考 文 献 34

致 谢 35

|