基于FPGA的四路抢答器的设计(附Verilog_HDL代码)

来源:56doc.com 资料编号:5D11010 资料等级:★★★★★ %E8%B5%84%E6%96%99%E7%BC%96%E5%8F%B7%EF%BC%9A5D11010

资料介绍

基于FPGA的四路抢答器的设计(附Verilog_HDL代码)(10000字)

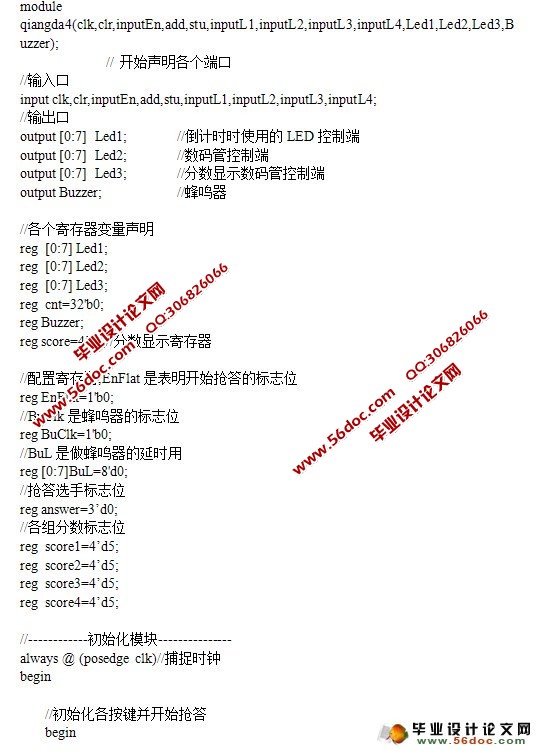

摘要 本文介绍了一种基于VHDL语言,采用FPGA芯片作为控制核心,设计的一款智力竞赛抢答器,且给出了各模块及具体电路图。并利Altera公司的开发平台MAX+PLUSⅡ工具完成了编译和仿真,经实际电路测试验证,达到了预期的设计要求。随着我国经济和文化事业的发展,在很多公开竞争场合要求有公正的竞争裁决,诸如证券、股票交易及各种智力竞赛等,因此出现了抢答器。抢答器一般是由很多电路组成的,线路复杂,可靠性不高,功能也比较简单,特别是当抢答路数很多时,实现起来就更为困难。因此我们设计了以FPGA器件的新型智能的抢答器,在保留了原始抢答器的基本功能的同时又增加一系列的实用功能并简化其结构。FPGA的抢答器又称为第一信号鉴别器,其主要应用于各种知识竞赛、文艺活动等场合。 FPGA技术正处于高速发展时期,新型芯片的规模越来越大,成本也越来越低,低端的FPGA已逐步取代了传统的数字元件,高端的FPGA不断在争夺ASIC的市场份额。基于FPGA的开发成为一项系统级设计工程。随着半导体制造工艺的不同提高,FPGA的集成度将不断提高,制造成本将不断降低,其作为替代ASIC 来实现电子系统的前景将日趋光明。

关键词:FPGA Max+plusⅡ 多路抢答器 VHDL

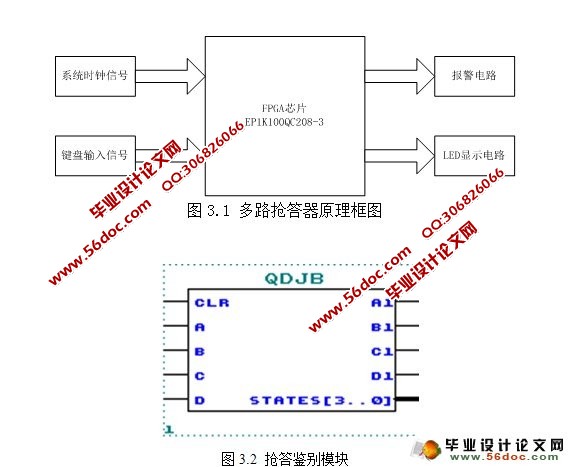

抢答器的原理框图如图3.1所示,其核心采用FPGA芯片作为控制系统,秒脉冲信号作为系统时钟信号,主要用于系统计时,主持人复位按钮、选手抢答按钮以及各组选手加、减分控制器均由键盘输入,通过LED显示电路显示抢答组别代码和每组选手得分情况,并用扬声器响声来确定抢答成功和抢答犯规。

此模块的作用为当主持人按下开始按钮,即CLR为复位后,为低电平时有效,抢答开始,A,B,C,D为选手开始抢答,高电平有效,最后鉴别出谁是最先抢答的,是有效的抢答。这就是抢答鉴别模块的作用。

目录

第一章 设计的工具与平台 5

1.1 EDA的技术[1]-[3] 5

1.1.1 EDA技术的起源 5

1.1.2 什么叫EDA技术[4] 5

1.1.4 EDA技术的主要内容 6

1.1.5 EDA技术的应用形式 7

1.2 FPGA简介[5]-[7] 7

1.2.1 FPGA设计背景 7

1.2.2 FPGA基本结构和特点 8

1.2.3 课题研究的意义 9

1.3 VHDL语言的概述[8]-[12] 9

1.3.1 VHDL的简介 9

1.3.2 VHDL的优点 10

1.3.3 VHDL语言的开发流程 10

1.4 MAX+PLUS软件的简介 11

1.4.1 Max+plusⅡ的概述[13] 11

1.4.2 Max+plusⅡ的特点[14] 11

1.4.3 Max+plusⅡ的功能简介 12

第二章 多路抢答器设计与分析 15

2.1 系统设计基本要求 15

2.2 系统设计方案 15

2.3 系统的组成及工作原理 16

第三章 系统整体的结构和各个组成的模块 17

3.1 系统的结构 17

3.2抢答鉴别模块 17

3.3 计分电路模块 18

3.4 计时电路模块 18

3.5 译码电路模块 19

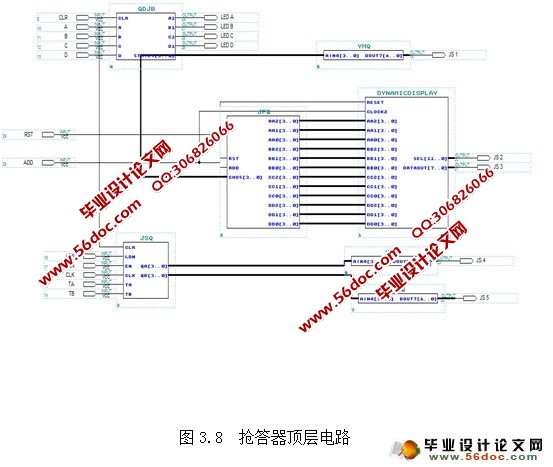

3.6 抢答器顶层电路 20

第四章 系统仿真 23

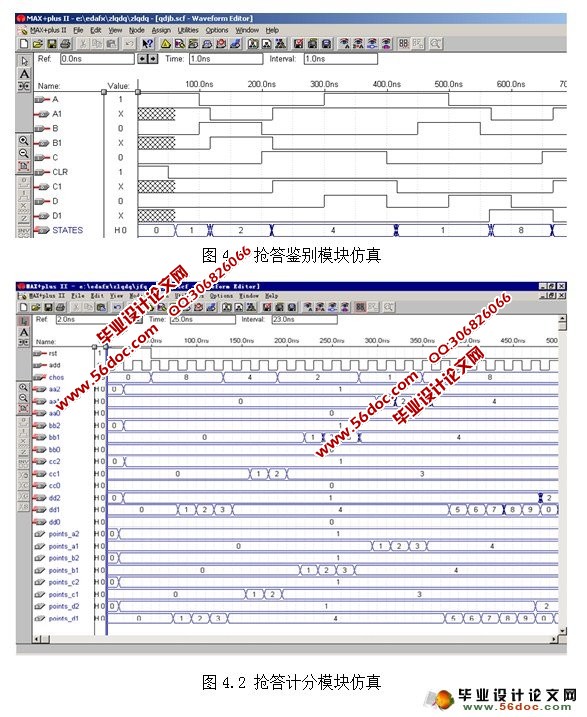

4.1 抢答器鉴别模块仿真 23

4.2 抢答计分模块仿真 23

4.3 抢答器计时模块仿真 24

4.4 静态译码器电路模块仿真 25

4.5 动态译码器电路模块仿真 25

第五章 结论 27

致谢 29

参考文献 31

附录A 程序代码 33 |