ЛљгкFPGAЕФаХКХдДЩшМЦ(ТлЮФ14000зж)

еЊвЊЃКБОЮФЪзЯШНщЩмСЫаХКХдДЕФбаОПБГОАКЭDDSММЪѕЕФРэТлЃЌШЛКѓИљОнБОПЮЬтФПБъКЭФкШнЃЌНсКЯ DDSММЪѕЃЌНшжњИпМЏГЩЖШЕФ FPGAаОЦЌЃЌвРПП Quartus IIКЭ Nios IIМЏГЩПЊЗЂЛЗОГЦНЬЈЃЌЪЙгУ verilogгВМўУшЪігябдКЭ CгябдГЬађБрГЬЃЌЪЕЯжвЛПюИпОЋЖШЁЂЕЭГЩБОЁЂЖрЙІФмЁЂБуаЏЪНЁЂИпадМлБШЕФаХКХЗЂЩњЦїЁЃТлЮФЯъЯИВћЪіСЫдкQuartusЂђЛЗОГжаРћгУVerilog HDLгябдЩшМЦаХКХЗЂЩњЦїЕФЙ§ГЬЃЌЪЕЯжВЈаЮЧаЛЛЁЂШЮвтЦЕТЪКЭЗљЖШПЩЕїЕФЙІФмЃЌВЂИјГіСЫЯргІЕФВтЪдНсЙћЁЃЪЕбщНсЙћБэУїЃЌРћгУFPGAЪЕЯжDDSММЪѕДгЖјжЦдьГіаХКХдДЕФЗНАИЪЧЧаЪЕПЩааЃЌОпгаЬхаЭаЁЁЂГЩБОЕЭЁЂОЋЖШИпЕШгХЕуЃЌЪЧаХКХЗЂЩњЦїЮДРДЕФЗЂеЙЗНЯђЁЃ

ЙиМќДЪЃКаХКХдДЃЛFPGAЃЛDDSММЪѕЃЛverilogгябд

Design and Implementation of Signal Source Based on FPGA

AbstractЃКThis paper first introduces the research background of the signal source and the theory of DDS technology. Then, according to the goal and content of this project, combined with DDS technology, with highly integrated FPGA chip, relying on Quartus II and Nios II integrated development environment platform, using verilog hardware description Language and C language programming, to achieve a high-precision, low-cost, multi-functional, portable, cost-effective signal generator. In this paper, the process of designing the signal generator in Verilog HDL language in Quartus Ђђ environment is described in detail, and the function of waveform switching, arbitrary frequency and amplitude is realized, and the corresponding test results are given. The experimental results show that it is feasible and feasible to implement DDS technology to realize the signal source by using FPGA. It has the advantages of small size, low cost and high precision, and is the future development direction of signal generator.

Key wordsЃКSignal sourceЃЛFPGAЃЛDDS technologyЃЛVerilog language

ФП ТМ

1ЁЂаїТл 1

1.1ЁЂПЮЬтБГОА 1

1.2ЁЂаХКХЗЂЩњЦїЕФЙІФм 1

1.3ЁЂЙњФкЭтаХКХдДЕФЗЂеЙЯжзД 2

1.4ЁЂаХКХдДЕФЗЂеЙЧїЪЦМАбаОПвтвх 3

1.5ЁЂПЮЬтбаОПФкШнМАФПБъ 4

2ЁЂ DDSаХКХЗЂЩњЦїРэТлЗжЮі 5

2.1ЁЂЦЕТЪКЯГЩММЪѕМђНщ 5

2.2ЁЂDDSЛљБОдРэКЭНсЙЙЬиЕу 5

2.2.1ЁЂDDSЛљБОНсЙЙ 5

2.2.2ЁЂDDSЛљБОдРэ 7

2.2.3ЁЂDDSЙЄзїЬиЕу 8

2.3ЁЂDDSШЮвтВЈаЮЕФВњЩњ 9

2.4ЁЂDDSММЪѕЕФЙЄзїжИБъ 10

3ЁЂ ЛљгкFPGAЕФDDSЯЕЭГЪЕЯж 11

3.1ЁЂFPGAМђНщ 11

3.2ЁЂFPGAПЊЗЂЛЗОГМђНщ 11

3.3ЁЂаХКХЗЂЩњЦїЕФFPGAЪЕЯж 12

3.3.1ЁЂЩшМЦФЃПщЛЎЗж 13

3.3.2ЁЂЪБжгФЃПщЕФЩшМЦ 13

3.3.3ЁЂЯрЮЛРлМгЦїФЃПщЕФЩшМЦ 14

3.3.4ЁЂВЈаЮДцДЂЦїФЃПщЕФЩшМЦ 15

3.3.5ЁЂВЈаЮбЁдёФЃПщЕФЩшМЦ 18

3.3.6ЁЂDAзЊЛЛФЃПщ 19

3.4ЁЂаОЦЌв§НХЖЈвх 20

3.5ЁЂЩшМЦНсЙћБЈИц 20

4ЁЂ ЯЕЭГадФмВтЪдгыЮѓВюЗжЮі 22

4.1ЁЂгВМўЕїЪд 22

4.2ЁЂЪфГіВЈаЮ 22

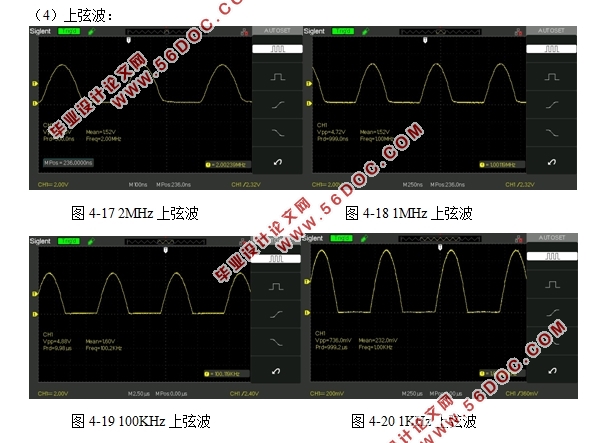

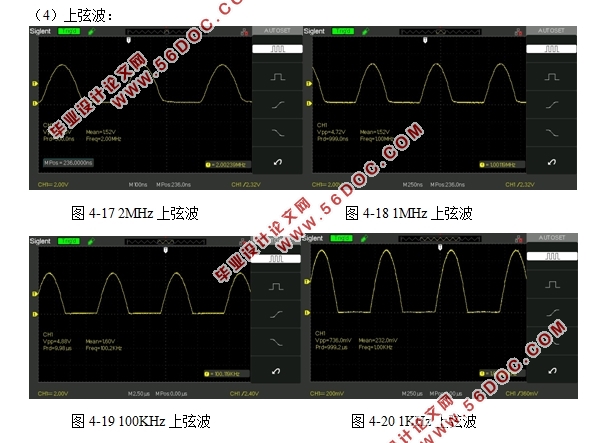

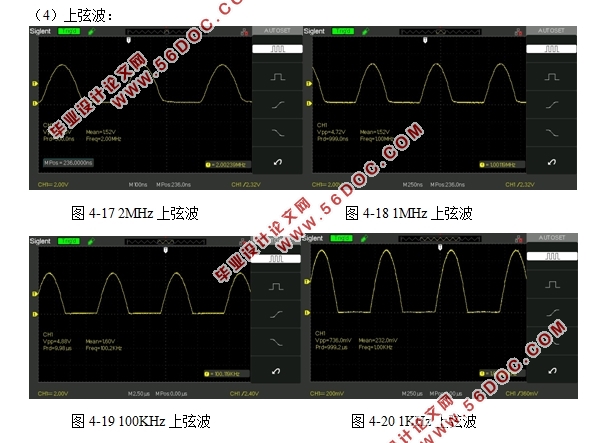

4.3ЁЂадФмжИБъ 24

4.4ЁЂЪЕЮяеЙЪО 25

5ЁЂзмНсгыеЙЭћ 27

ВЮПМЮФЯз 28

жТаЛ 29

|