ЛљгкFPGAЕФЮоЯпЪ§ОнВЩМЏЯЕЭГЩшМЦ

РДдДЃК56doc.com зЪСЯБрКХЃК5D26834 зЪСЯЕШМЖЃКЁяЁяЁяЁяЁя %E8%B5%84%E6%96%99%E7%BC%96%E5%8F%B7%EF%BC%9A5D26834

зЪСЯвдЭјвГНщЩмЕФЮЊзМ,ЯТдиКѓВЛЛсгаЫЎгЁ.зЪСЯНіЙЉбЇЯАВЮПМжЎгУ. Ум БЃ Лн Аяжњ

зЪСЯНщЩм

ЛљгкFPGAЕФЮоЯпЪ§ОнВЩМЏЯЕЭГЩшМЦ(ШЮЮёЪщ,ПЊЬтБЈИц,ТлЮФ14300зж)

еЊ вЊ

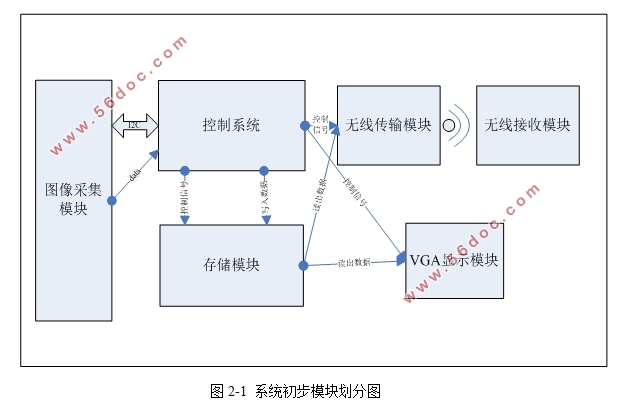

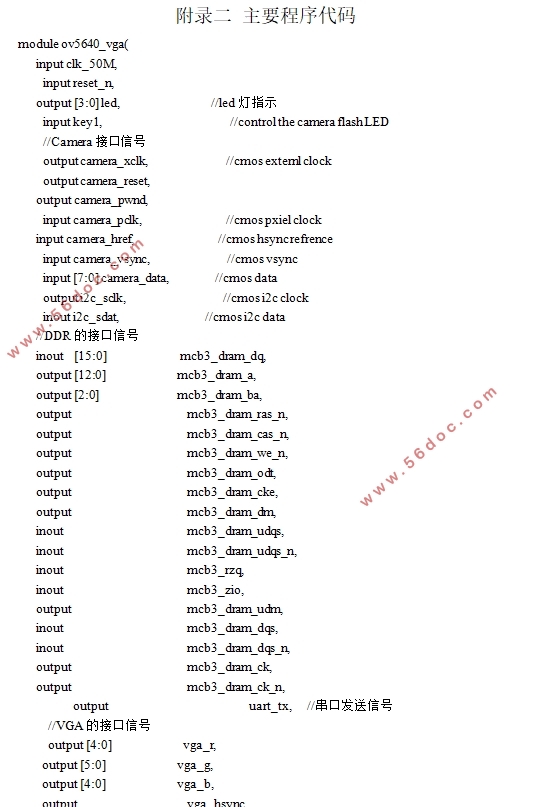

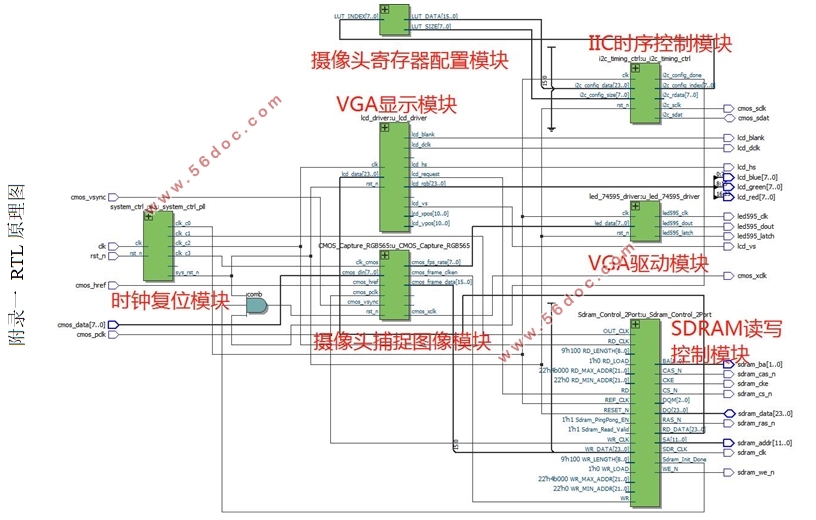

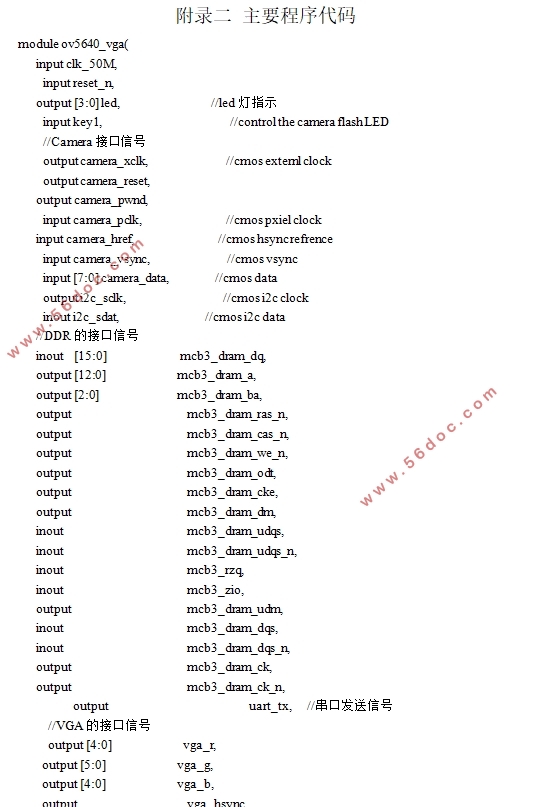

ЛљгкFPGAЃЈField Programmable Gate ArrayЃЉЕФЭМЯёДІРэПЫЗўСЫЖЈжЦЕчТЗСщЛюадВюЃЌЮоЯпЭМЯёДЋЪфДцдкЕФЪ§ОнСПЙ§ДѓЁЂДЋЪфДјПэЪмЯоЕШШБЕуЃЌОпБИИпЫйВЂааЕФЬиЕуЃЌЬсГівЛжжЛљгкFPGA+ZigBeeЕФЭМЯёВЩМЏМАЮоЯпЪ§ОнДЋЪфЗНАИЃЌгааЇРћгУFPGAСщЛюадЧПЕФгХЪЦПЩвдЗНБуКѓајНјааЭМЯёДІРэЫуЗЈЕФбщжЄЙЄзїЁЃБОЮФЪЙгУXilinxЙЋЫОЕФISEШэМўНјааПЊЗЂЃЌВЩгУVerilogгВМўУшЪігябдЪЕЯжНгПкгыИїЙІФмФЃПщЕФгВМўЛЏЃЌгУOV5640зїЮЊЭМЯёВЩМЏЯЕЭГЃЌВЩМЏЕНЕФЭМЯёЪЕЪБДцЗХдкDDR3 SDRAMжаЃЌFPGAПижЦВЩгУ“ЦЙХвВйзї”ПижЦЭМЯёЪ§ОнЕФЪЕЪБаДШыгыЖСГіЃЌВЂЧ§ЖЏVGAЪЕЪБЖСГіЭМЯёЪ§ОндкЯдЪОЦїжаНјааЯдЪОЃЌЭМЯёЪ§ОнЭЈЙ§ZigBeeДЋЕНЩЯЮЛЛњжаЃЌЭЈЙ§ДЎПкЕїЪджњЪжЯдЪОНгЪеЕНЕФЭМЯёЪ§ОнЁЃ

ЙиМќДЪЃКFPGA ЭМЯёВЩМЏ ЮоЯпДЋЪф ZigBee

Design of Wireless Data Acquisition System Based on FPGA

Abstract

Image processing based on FPGA (Field Programmable Gate Array) overcomes the disadvantages of poor custom circuit flexibility, large amount of data in wireless image transmission, and limited transmission bandwidth. It has the characteristics of high-speed parallelism and proposes an image based on FPGA+ZigBee. The acquisition and wireless data transmission scheme can effectively utilize the advantage of FPGA flexibility to facilitate the subsequent verification of image processing algorithms. This article uses Xilinx's ISE software development, using Verilog hardware description language to achieve the hardware interface and various functional modules, using OV5640 as an image acquisition system, the captured image is stored in DDR3 SDRAM in real time, FPGA control using "ping pong operation" Control the real-time writing and reading of the image data, and drive the VGA to read the image data in real time and display it on the display. The image data is transmitted to the upper computer through ZigBee, and the received image data is displayed through the serial debugging assistant.

Keywords: FPGA; image acquisition; wireless transmission; ZigBee

ФПТМ

еЊвЊ I

ABSTRACT II

ЕквЛеТ аїТл 1

1.1 ПЮЬтБГОАгывтвх 1

1.2 ЭМЯёВЩМЏгыДЋЪфЕФЗЂеЙЯжзДКЭЧїЪЦ 1

1.2.1 ЙњФкЭтбаОПЗЂеЙзДПі 1

1.2.2 ЭМЯёВЩМЏгыЮоЯпЪ§ОнДЋЪфЕФЗЂеЙЧїЪЦ 2

1.3 FPGAММЪѕИХПі 3

1.4 ПЮЬтШЮЮё 4

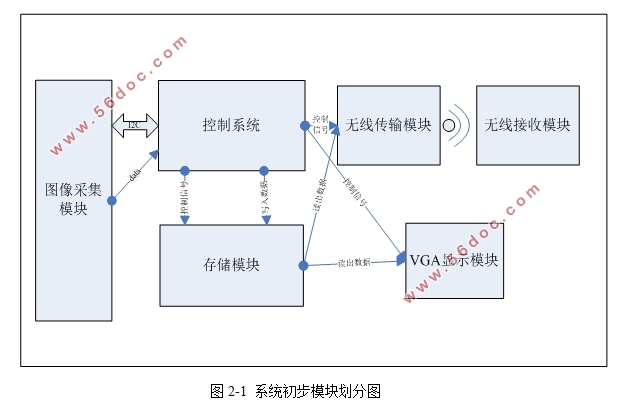

ЕкЖўеТ ЮоЯпЪ§ОнВЩМЏЯЕЭГзщГЩМАЦїМўбЁаЭ 6

2.1 ЯЕЭГФЃПщЛЎЗж 6

2.2 ФЃПщЦїМўбЁдёЗНАИ 7

2.2.1 ЭМЯёВЩМЏФЃПщ 7

2.2.2 ДцДЂФЃПщ 8

2.2.3 ЮоЯпДЋЪфФЃПщ 10

ЕкШ§еТ ПижЦЯЕЭГЩшМЦ 12

3.1 ПижЦЯЕЭГзмЬхЩшМЦПђЭМ 12

3.2 ЯЕЭГИїФЃПщЩшМЦЗНЗЈ 13

3.2.1 OV5640ЩЯЕчЕШД§ФЃПщЩшМЦ 14

3.2.2 МФДцЦїХфжУФЃПщЩшМЦ 16

3.2.3 ЭМЯёВЩМЏФЃПщЩшМЦ 19

3.2.4 DDR3ЖСаДПижЦФЃПщЩшМЦ 21

3.2.5 VGAЭМЯёЯдЪОФЃПщЩшМЦ 26

3.2.6 ЮоЯпЪ§ОнДЋЪфФЃПщЩшМЦ 28

3.2.7 ЪБжгИДЮЛЙмРэФЃПщ 31

ЕкЫФеТ ЯЕЭГЕїЪд 33

4.1 гВМўЦНЬЈДюНЈ 33

4.2 ЪЕбщЯжЯѓ 34

ЕкЮхеТ змНсгыеЙЭћ 36

5.1 змНс 36

5.2 еЙЭћ 36

ВЮПМЮФЯз 38

жТаЛ 40

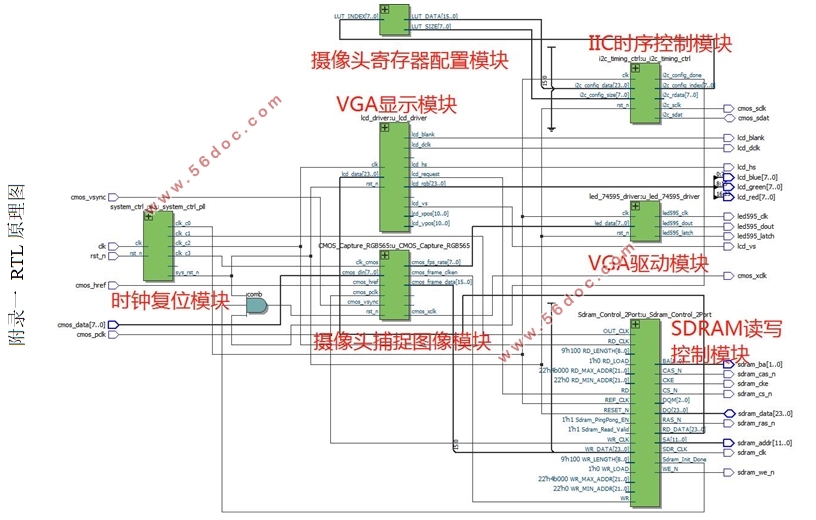

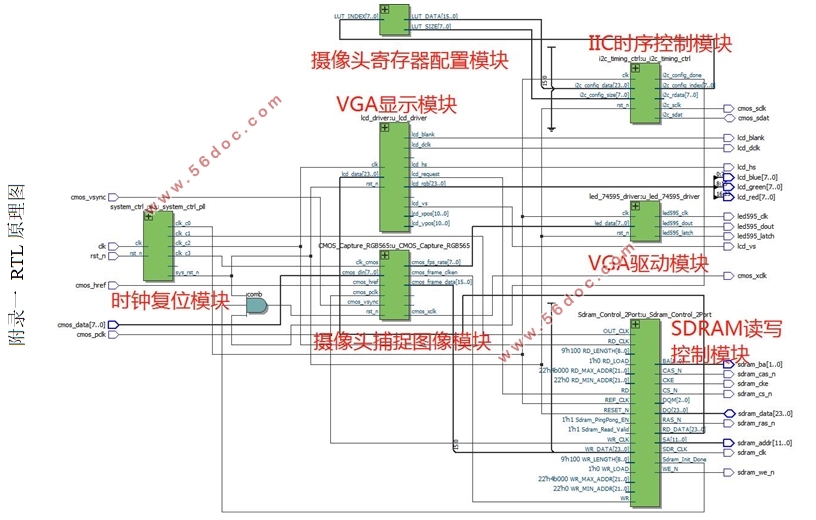

ИНТМвЛ RTLдРэЭМ 41

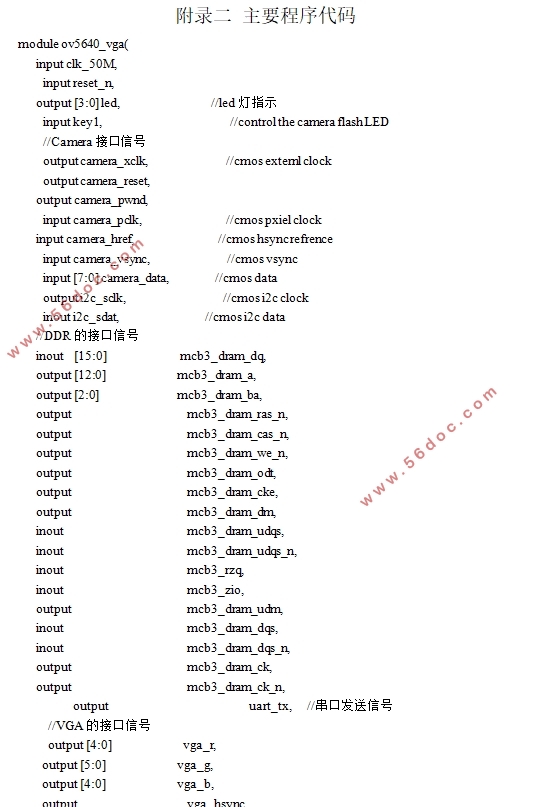

ИНТМЖў жївЊГЬађДњТы 42

|